(5D 4 G 11 C 29/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

## ОПИСАНИЕ ИЗОБРЕТЕНИЯ

**Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ**

- (21) 4025434/24-24

- (22) 21.02.86

- (46) 07.07.87. Бюл. № 25

- (71) Минский радиотехнический институт

(72) Н. И. Урбанович и П. П. Урбанович

(53) 681.327.6 (088.8)

- (56) Авторское свидетельство СССР № 733034, к.т. G 11 C 29/00, 1977. Авторское свидетельство СССР

- № 1059629, кл. G 11 C 29/00, 1983.

## ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

(57) Изобретение относится к вычислительной технике и может быть исполь-зовано при создании систем памяти с по-вышенной функциональной надежностью. Целью изобретения является повышение надежности устройства. Устройство содержит основной накопитель, первый и второй

коммутаторы, первый и второй формирователи паритетных символов, первый и второй формирователи контрольных символов, первый и второй дополнительные накопители, первый и второй блоки коррек-ции, первый, второй, третий и четвертый блоки сравнения, блоки обнаружения корректируемых и некорректируемых ошибок, корректор информации, блок исправления ошибок, блок вывода информации. В устройстве обеспечивается коррекция многократных ошибок, распределенных таким образом, что в любом столбце и в любой строке основного накопителя должно находиться не более одного неисправного элемента памяти. Блоки коррекции обеспечивают исправление ошибок, вызванных неисправностями формирователей паритетных и контрольных символов или дополнительных накопителей. 1 з. п. ф-лы, 5 ил.

Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти с повышенной функциональной надежностью.

Пель изобретения повышение надежности устройства.

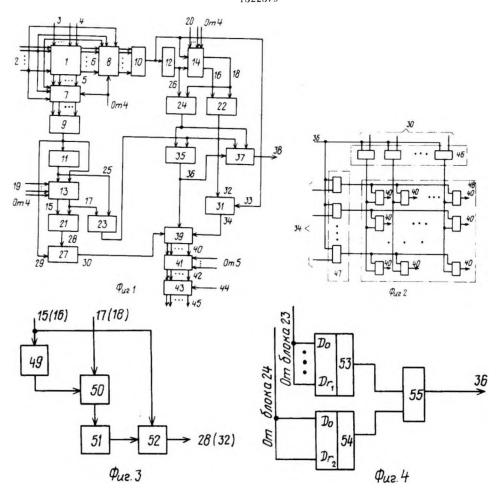

На фиг. 1 язображена схема запоминающего устройства (ЗУ) с самоконтролем; на фиг. 2 — схема корректора информации; на фиг. 3 — схема блока коррекции; на фиг. 4 — схема блока обнаружения корректируемых ошибок; на фиг. 5 — схема блока обнаружения некорректируемых опибок.

ЗУ с самоконтролем (фиг. 1) содержит основной накопитель 1 с информационными 2. адресными 3 и управляющим 4 входами, первыми 5 и вторыми 6 выходами, первый 7 и второй 8 коммутаторы, первый и второй 10 формирователи паритетных символов, первый 11 и второй 12 формирователи контрольных символов, первый 13 и второй 14 дополнительные накопители с выходами 15 - 18 и входами 19 и 20, вервый 21 и второй 22 блоки коррекции, первый 23 и второй 24 блоки сравнения, первые входы 25 блока 23 в первые входы 26 блока 24. третий блок 27 сравнения с первыми 28 и вторыми 29 входами и выходами 30, четвертый блок 31 сравнения с первыми 32 и вторыми 33 входами и выходами 34, блок 35 обнаружения корректируемых (одиночных) ошибок, выход 36 блока 35, блок 37 обнаружения некорректируемых ошибок, выход 38 блока 37, корректор 39 информации. выходы 40 которого подключены к одним входам блока 41 исправления опшбок, вы ходами 42 подключенного к входам блока 43 ввода информации, управляющий вход а выходы блока 43, подключенные соответственно к второму управляющему входу 44 устройства в к его информационным выходам 45.

Корректор 39 информации содержит (фиг 21 первую группу 46 элементов И, вторую группу 47 элементов И, матрицу 48 элементов И.

Блоки 21 и 22 коррекции, (фиг. 3) содержат сумматоры 49 по модулю два, формирую щие повые конгрольные символы, схему 50 вычисления синдрома, декодер 51, сумматоры 52 по молулю два.

Блок 35 обнаружения корректируемых опибок (фиг. 4) содержит дополнительные сумматоры 53 и 54 по модулю два и элемент И 55.

Блок 37 обнаружения некорректируемых опибок (фиг. 5) содержит элемент ИДИ 56 и элемент И 57.

Накопители 1, 13 и 14 представляют собой матрицу элементов намяти (ЭП) со схемами, обеспечивающими запись, хранение и считывание информации. Накопитель 1 содержит  $k_1$  столбцов и  $k_2$  строк. По

строкам размещены информационные биты, входящие в отдельные байты, по столбцам одноименные биты отдельных байт.

Формирователи 9 и 10 паритетных символов состоят из сумматоров по модулю два, осуществляющих сложение битов информации, записываемых в ЭП соответствующего столбна или соответствующей строки (свертпо модулю два). Формирователи и 12 контрольных символов также состоят вз сумматороч по модулю два в производят формирование контрольных символов применяемого кода на основании паритетных символов. Блоки 23 и 24 сравнения состоят из сумматоров по модулю два по числу контрольных символов. Блоки 27 и 31 сравнения содержат соответственно k+ и k2 сумматоров по модулю два. Блок 41 исправления опибок состоит из сумматоров помолулю два, число которых равно количеству считываемой виформации (битов)

Устройство работает следующим образом. При записи информации в пакопитель 1 формирователи 9 и 10 производят сложение по модулю два соответствующих битов информации, поступающих через соответствующие коммутаторых поступает, например, сигнал логической едиппы. Формирователи 11 и 12 по сформированным k и  $k_2$  паритетным симводам вычисляют соответственно  $r_1$  р  $r_2$  контрольных симводов. Сформированные таким образом кодовые слова записываются соответственно в накопители 13 и 14.

В режиме считывания информации из накопителя І формирователи 9 осуществляют формирование, как и в режиме записи, паритетных и соответствующих им контрольных символов. При появлении ошибок отмеченные гары соответствую щих контрольных и наризетных битов будут отличаться. Блоки 21 в 22 воестанавливают истинное значение паритетных символов В блоках 23 и 21 сравмения прочитанные контрольные символы (r в r) поразрядно сравниваются с вновь сформированными контрольными битами. Причем, если в информационных битах имеется не более одной ошибки в любом столбие и строке накоинтеля, то соответс вующие пары контрольных символов будут отличаться. Об этом будет свидетельствовать единичный сигнал на выходе 36 блока 35. Если же в какойдибо строке или столбце появятся два неисправных ЭП, то это будет отмечено единичным сигналом на выходе 38 блока 37 Шина этого сигнала соеднияется с процессором (не показан) для прерывания выполнения команды и принятия мер к устранению двойной ошибки. На выходах блока 27 сравнения и на выходах 34 блока 31 сравнения вырабатываются векторы ошибок по строкам и по столбцам. Единичные сигналы будут установлены в тех

2

разрядах векторов, соответствующие которым столбцы и строки накопителя 1 содержат неисправные ЭП. Корректор 39 вырабатывает сигиалы коррекции информационных бит (на выходах 40), которые поступают на один входы сумматоров по модулю два блока 41, и инвертированием ошибочных бит считываемой информации, поступающей на другие входы соответствующих сумматоров блока 41, исправляют все одиночные оппибки, которые возникают в отдельных строках и столбцах наколителя Информация без ошибок с выходов блока 41 поступает в блок 43 ввода информации и по поступлении на управляющий вход 41 этого блока соответствующего управляющего сигнала на информационные выходы 45 устройства.

## Формула изобретения

Запоминающее устройство с самоконтролем, содержащее основной накопитель, информационные входы которого соединены с информационными входами первой группы первого и второго коммутаторов в являются информационными входами устройства, адресные входы основного накопителя являются адресными входами первой группы устройства, вход записи считывания устройства является входом записи считывания и соединен с входами записи считывания первого и второго дополнительных накопителей и с управляющими входами первого и второго коммутаторов, информационные входы второй группы которых подключены соответственно к выходам первой и второй групп основного накопителя, а вы ходы соединены с входами соответственно первого и второго формирователей паритетных символов, выходы которых подключены соответственно к входам первого и второго формирователей контрольных символов, выходы которых соединены соответственно с виформационными входами первой группы первого дополантельного накопителя и первого блока сравнения и с информационными входами первой групны второго дополнительного накопителя и второго блока сравнения, адресные входы первого и второго дополнительных накопителей являются соответственно адресными входама второй ч третьей групп устройства, а выходы первой группы полключены соответственно к информационным входам второй группы иср.

вого и второго блоков сравнения, выходы которых соединены соответственно с входами первой и второй групп блоков обпаружения корректируемых и некорректируемых ошибок, выход блока обнаружения корректируемых онибок соединей с входами выборки копректора виформации в блока обпаружения некорректируемых ошибок, выход которого является выходом ошибки устройства,выходь корректора информации водключены к входам коррекции блока исправления опибок. информационные входы которого соединены с выходами первой группы основного изковителя, а выходы подключены к информашионным входам блока вывода информации, управляющий вход и выходы которого являются соответственно входом разрешения считывания и информационными выходами устройства, отличающееся тем, что, е ненью повышения надежности устройства, в него введены первый и второй блоки коррекции, третий и четвертый блоки сравнения, причем входы первой группы третьего и четвертого блоков сравнения соединены соответственно с выходами первого и вто рого блоков коррекции, входы которых подключены к выходам соответственно первого н второго дополнительных накопителей, входы второй группы третьего блока сравнения сосдинены с выходами первого формирователя парителных символов и с виформационнымя входами второй группы первого до-полнительного накопителя, входы второй трушны четвертого блока спавнения полключены в выходам второго формирователы нарателям свяволов в к виформационным вхолюм второй трункы второго доролнитель Вого наконителя выхолы третьего и четвер того блоков гравнения соединены с информационечми входеми первой и второй групп корректега информации.

3 Устроиство по п. 1, отдинающееся тем, то зоррестор информацие содержит магрялу стемен ов 41, первые и вторые выходы лиорых соединены соответственно с выходым дементов И первои и второи групп, а выходы являются выходы элементов И вервой в второй групп являются соот ветственно информационными входами нервой а второи рли корректора информации, а люорое пходы элементов И первой и второи групп являются соот вогственно информационными входами нервой а второи рли корректора информации, а люорое пходы являются входами выборки корректоры информации.

Редактор С. Пекарь Техрел И. Верес Корректор С. Черии Заказ 2873.50 Тираж 589 Подинское

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж. 35, Раушская наб., д. 4/5

Производственно поляграфическое предприятие, г. Ужгород, ул. Проектная, 4