## (19) <u>SU (11)</u> 1725261 A1

(51)5 G 11 C 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ ПРИ ГКНТ СССР

## ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1

(21) 4798119/24

(22) 23.01.90

(46) 07.04.92. Бюл. № 13

(71) Минский радиотехнический институт

(72) П.П.Урбанович и С.Л.Лойка

(53) 681.327.6(088.8)

(56) Патент ФРГ № 2549392,

кл. G 11 С 8/00, опублик. 1977.

Авторское свидетельство СССР № 1026165, кл. G 11 C 29/00, 1982.

(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С

АВТОНОМНЫМ КОНТРОЛЕМ

(57) Изобретение относится к вычислительной технике и может быть использовано в электронной промышленности при изготовлении больших интегральных схем запоми-

нающих устройств повышенной надежности. Целью изобретения является упрощение устройства. Устройство содержит основной 1 и дополнительный 2 блоки памяти, дешифратор 4 адреса строк, дешифратор 6 адреса разрядов, группу элементов И 9, первый 10 и второй 36 сумматоры по модулю два, группу 11 сумматоров по модулю два, группу 11 сумматоров по модулю два, регистр 12, блок 16 кодирования, блок 18 управления, основной 25 и дополнительный 26 блоки считывания, блок 29 вычисления синдрома, блок 32 анализа ошибок, элемент И 34, блок 37 выдачи информации. Устрой-

ство обеспечивает исправление ошибок только в тех символах кодового слова, которые считываются в данном цикле. 2 ил.

Puz.1

Изобретение относится к вычислительной технике и может быть использовано в электронной промышленности при изготовлении больших интегральных схем запоминающих устройств (БИС ЗУ), а именно при изготовлении БИС ЗУ, имеющих большую площадь кристаллов, где требуется увеличить выход правильно функционирующих устройств, а также при создании систем панадежности хранения информации.

Известно ЗУ с автономным контролем, содержащее основной и дополнительный накопители, два блока кодирования, блоки считывания информации, управления, конт- 15 роля и исправления ошибок.

Устройство обеспечивает повышение надежности хранения информации за счет коррекции ошибок, однако обладает сравнительно большой структурной избыточно- 20 стью из-за наличия двух идентичных блоков кодирования, что снижает его належность.

Наиболее близким по технической сущности к предлагаемому является ЗУ с автономным контролем, содержащее 25 накопитель, числовые шины которого соединены с выходами дешифратора адреса строк, а выходные шины - с информационными входами первого блока считывания, выходами первых вентилей и информационными входами второго блока считывания, выходами вторых вентилей соответственно. первые и вторые входы первых и вторых вентилей подключены к шинам разрешения записи и управления, третьи их входы - к шине записи и выходам блока кодирования соответственно, четвертые входы первых вентилей связаны с выходами дешифратора адреса разрядов, управляющими входами первого блока считывания и первыми управ- 40 ства. ляющими входами выходного блока, выходы второго блока считывания соединены с первыми входами первых сумматоров по модулю два, выходы которых являются входами блоха анализа отказов, выходами соединенного с первыми входами вторых сумматоров по модулю два, вторые входы вторых сумматоров по модулю два соединены с первыми выходами первого блока считырания, а выходы вторых сумматоров по 50, модулю два связаны с информационными входами выходного блока, вторые управляющие входы которого соединены с шинами разрешения записи, управления и записи, первые входы третьих вентилей подключе- 55 ны к выходным шинам дешифратора адреса разрядов, вторые входы третьих вентилей соединены с выходом третьего сумматора по модулю два, первый и второй входы которого соединены с шиной записи и вторым

выходом первого блока считывания соответственно, выходы третьих вентилей подключены к вторым входам регистра, первые входы которого соединены с первыми выходами первого блока считывания, а выходы его - к входам блока кодирования, выход которого подключен к вторым входам первых сумматоров по модулю два.

В известном устройстве обеспечиваетмяти, удовлетворяющих заданному уровню 10 ся обнаружение и исправление одной ошибки в строке основного и дополнительного накопителей при использовании кода Хемминга. При этом вне зависимости от разрядности ЗУ (одно- или многоразрядная) в режиме записи или считывания информации из основного накопителя осуществляются манипуляции над разрядами всей строки основного накопителя и соответствующей строки дополнительного накопителя (основная строка состоит из к разрядов, дополнительная из г). Необходимость обработки в режиме записи при рассматриваемом алгоритме функционирования ЗУ очевидна. Однако если устройство является одноразрядным, исправление ошибки в режиме считывания информации в том разряде слова, который в данном цикле не считывается на выход ЗУ, практического смысла не имеет. Достаточно обнаружить и исправить ошибку в том разряде строки, который считывается именно на выход устройства, т.е. важно предусмотреть, чтобы ошибочный разряд не попал на выход ЗУ.

Таким образом, реализация алгоритма функционирования известного ЗУ приводит к его усложнению и снижению общей надежности.

Цель изобретения - упрощение устрой-

Поставленная цель достигается тем, что в ЗУ с автономным контролем, содержащее основной и дополнительный накопители. числовые шины которых соединены с выходами дешифратора адреса строк, а выходные шины - с информационными входами соответственно основного и дополнительного блоков считывания, информационный вход основного накопителя подключен к информационному входу устройства, связанному также с одним входом первого сумматора по модулю два, второй вход которого соединен с первым выходом основного блока считывания, а выход – с одними входами первых элементов И, вторые входы которых связаны с соответствующими выходами дешифратора адреса разрядов, подключенными также к разрядным шинам основного накопителя и управляющим входам основного блока считывания, вторые выходы которого соединены с одними входами соответствующих вторых сумматоров по модулю два, вторыми входами связанных с выходами соответствующих первых элементов И, а выходами - с соответствующими информационными входами регистра. выходы которого соединены с входами блока кодирования, выходами подключенного к информационным входам дополнительного 10 накопителя и к одним входам блока вычисления синдрома, вторые входы которого связаны с выходами дополнительного блока считывания, управляющие входы основного и дополнительного накопителей соединены с выходом блока управления, подключенным также к одному входу выходного блока, второй вход которого связан с выходом третьего сумматора по модулю два, один вход которого соединен с первым выходом основного блока считывания, входы дешифратора адреса разрядов и дешифратора адреса строк подключены к адресным входам устройства, входы блока управления - к первому и второму управляющим входам устройства, управляющий вход регистра - к третьему управляющему входу устройства, третий вход первых элементов И - к четвертому управляющему входу устройства, выход выходного блока - к информационному выходу устройства, введены блока анализа и второй элемент И, выход которого соединен с вторым входом третьего сумматора по молулю два, а входы - с выходами блока анализа, одни входы которого связаны с выходами блока вычисления синдрома, другие - с входами дешифратора адреса разрядов, а третий вход - с одним управляющим входом устройства, причем блок анализа состоит из первых и 40 вторых сумматоров по модулю два, одни входы которых подключены к первым входам блока, другие входы первых сумматоров - к вторым входам блока, вторые входы других сумматоров по модулю два - к треть- 45 ему входу блока, а выходы первых и вторых сумматоров по модулю два соединены с вы-

Сущность изобретения заключается в исправлении ошибки только в считываемом 50 разряде кодового слова. При этом проверочная матрица кода строится так, чтобы при этом межно было использовать код адреса опрашиваемого разряда, как известно состоящего из всех нулевых символов, и собержащего один единичный символов любом разряде. Чтобы синдромы ошибок отличались, р разрядов означает, что коду 00...0 на входах дешифратора адреса разрядов соответствует первый вектор-столбец проверочной матрицы вида 00...011, а коду

00...01 – вектор-столбец 00...0111 и т.д., что позволяет определять местоположение ошибочного разряда без обычного дешифратора либо без используемой для этого в устройстве ПЛМ.

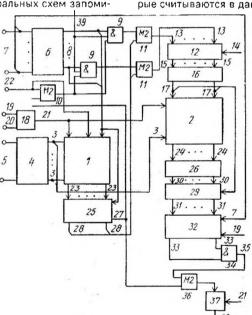

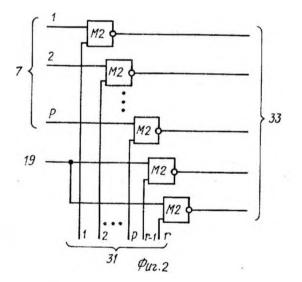

На фиг. 1 изображена структурная схема устройства; на фиг. 2 – функциональная схема блока анализа.

Устройство (фиг. 1) содержит основной 1 и дополнительный 2 блоки памяти, адресные входы строк 3 которых соединены с выходами дешифратора 4 адреса строк, входы которого соединены с одними адресными входами 5 устройства, дешифратор 6 адреса разрядов с входами 7 и выходами 8, группу элементов И 9, первый сумматор 10 по модулю два, группу сумматоров 11 по модулю два, группу сумматоров 11 по модулю два, регистр 12 с информационными входами 13 и входом 14 записи и выходами 15, блок 16 кодирования, выходы 17 которого подключены к информационным входам накопителя 2.

Устройство содержит также блок 18 управления представляющий собой элемент И, входы 19 и 20 которого соединены соответственно с первым и вторым управляющими входами устройства, а выход 21 блока 18 с управляющими входами накопителей 1 и 2. информационный 22 вход устройства, соединенный с сумматором 10 и информационным входом накопителя 1, выходы 23 и 24 накопителей 1 и 2 соответственно, основной 25 и дополнительный 26 блоки считывания, первый 27 и вторые 28 выходы блока 25 считывания, управляющие входы которого соединены с выходами 8 дешифратора 6, блок 29 вычисления синдрома, первые входы которого соединены с выходами 17 блока 16, а вторые входы - с выходами 30 блока 26, выходы блока 29, соединенные с первыми входами 31 блока 32 анализа, третий вход 33 которого подключен к шине 19 (CS). а выходы - к входам элемента И 34, выход 35 которого связан с одним входом второго сумматора 26 по модулю два, выход которого соединен с одним входом блока 37, доугой вход которого может быть соединен с выходом 21 блока 18 (этот вход блока 37 может при необходимости быть независимым от выхода 21 блока 18), выход 38 блока 37 является информационным выходом устройства, четвертый управляющий вход 39 устройства соединен с третьими входами элементов И 9.

Блок анализа 32 состоит из сумматоров по модулю два (фиг. 2).

Основной 1 и дополнительный 2 блоки памяти состоят из одинаковых элементов памяти (ЭП), которые хранят по одному разряду информации. Адресные дешифраторы.

8

блок управления - стандартные, как и в любой БИС ЗУ. Блоки считывания осуществляют считывание информации из строки в соответствии с кодом адреса на входах дешифратора адреса строк, к тому же на одном из выходов основного блока 25 считывания выделяется разряд строки в соответствии с кодом адреса на входах дешифратора адреса разряда. На входы блока управления подаются сигналы выборки кристалла (CS) и записи/чтения (WR/RD) (на вход блока может подаваться также входной информационный символ). Выходной блок может представлять собой обыкновенный управляемый вентиль. Блок кодирова- 15 осуществляет вычисление г проверочных символов кодового слова в соответствии с проволочной матрицей кода. Блок вычисления синдрома состоит из г сумматоров по модулю два, соединенных межсобой стандартным образом, характерным для блоков вычисления синдрома. Назначение остальных логических элементов - общепринятое.

Устройство работает следующим обра- 25 зом.

В режиме записи информации на входы дешифратора 4 адреса строк поступает код адреса опрашиваемой строки, в результате чего возбуждается одна из выходных шин 3 дешифратора 4, т.е. выбирается одна из строк. Информационные разряды (К) слова считываются по шинам 23 и поступают в первый блок 25 считывания и дальше с первых выходов 28 блока 25 поступают на входы 22 сумматоров 11 и далее — на входы 13 регистра 12 (на шине 39 — сигнал расрешия записи в регистр, например, "1").

Таким образом, k разрядов опрашиваемой строки переписываются в регистр 12. 40 Одновременно с этим на входы дешифратора 6 адреса разрядов поступает код адреса заряда, на пересечении которого со строкой находится опрашиваемый ЭП. Сигнал с одной из возбужденных шин 8 дешифратора 6. поступая на один из управляющих входов первого блока 25 считывания, вызывает появление на выходе 27 блока 25 информации (0 или 1), хранящейся в опрашиваемом ЭП. Этот сигнал поступает на вход сумматора 10 по модулю два и сравнивается с сигналом, установленным для записи в накопитель 1 на шине 22. Если сравниваемые сигналы отличаются, то на выходе сумматора 10 появляется единичный сигнал. Этот сигнал через вентиль 9, на первый вход которого действует единичный сигнал с возбужденной шины дешифрагора 6, поступает на вход соответствующего сумматора 11, т.е. разряд опрашиваемого слова проинверти-

руется. Если же записываемый в ЭП и хранящийся в нем символы совпадают, то изменения информации, считанной из строки, не происходит. На основании к информационных символов, хранящихся в регистре 21, блок 6 кодирования вырабатывает г проверочных символов, которые поступают на входы 17 накопителя 2. После этого на шине 20 появляется сигнал разрешения записи информации в ЭП, находящийся на пересечении выбранных строки и столбца накопителя 1, а также г проверочных символов в выбранную строку накопителя 2. На этом цикл записи окончен.

В режиме считывания в соответствии с кодом адреса опрашиваемой строки возбуждается одна из шин 3 дешифратора 4, и все ЭП этой строки подключаются соответственно через основные 23 и дополнительные 24 выходные шины накопителей 1 и 2 к ссновному 25 и дополнительному 26 блокам считывания. По считанным к информационным символам, поступающим в регистр 12 (на шине 38 - нулевой сигнал), в блоке 16 кодирования вырабатываются г новых проверочных символов, которые поступают на первые входы блока 29 и сравниваются в нем поразрядно с проверочными символами, поступающими на входы 30 блока 29 Если в считанном кодовом слове (k + r = h разрядов) нет ошибок, то синдром равен нулю, и на всех выходах 31 блока 29 будут уровни логического нуля. В противном случае - синдром нулю не равен. Все разряды синдрома поступают на первые входы соответствующих сумматоров по модулю два блока 32. На вторые входы одних из этих сумматоров поступает код адреса опрашиваемого из накопителя 1 разряда (по шинам 7), на другие входы других сумматоров блока 32 подается уровень логической единицы (это означает, что при числе разрядов в коде адреса опрашиваемого разряда І число проверочных разрядов корректирующего кода составляет r = 1+2 разрядов).

При совпадении соответствующих разрядов не равного нулю синдрома с кодом адреса опрашиваемого разряда (при условии совпадения двух остальных символов сравниваемых слов) устанавливается факт наличия ошибки в опрашиваемом разряде. При этом на всех выходах 33 блока 32 будут единичные сигналы, такой же сигнал будет и на выходе элемента И 34, которые проинвертирует ошибочный символ, поступающий на первый вход сумматора 36 с выхода 37 блока 25 считывания. Если синдром на выходах 31 блока 29 (I его разрядов) не совпадает с I разрядами кода адреса опрашиваемого разряда, это означает, что либо

ошибок нет, либо ошибка возникла в другом разряде слова (предусматривается, что ошибки большей кратности не возникают).

Рассмотрим для примера запись и считывание слова А = 1010 (в этом случае в строке располагаются четыре символа, k! = 4), тогда l = 2, r = 4. Проверочная матрица корректирующего кода имеет вид

Предложим, что слово А ранее хранилось в опрашиваемой строке накопителя 1. Производится обращение к 2-й ячейке (хранит 0) для записи нулевого символа. При этом на выходе соответствующего сумматора 10 будет нулевой сигнал. В регистр 12 записывается слово А без изменений. Блок 16 кодирования вырабатывает четыре про- 20 верочных символа в соответствии с проверочной матрицей: 0100. Слово П переписывается в накопитель 1 (точнее. один из символов этого слова), проверочные символы - в накопитель 2.

Если производится считывание этого же разряда (второго), а он стал ошибочным в силу отказа ЭП, считанное слово будет иметь вид: 1110. На основании этого блок 16 вырабатывает новые проверочные символы: 30 1111, поступающие на первые входы блока 30, на вторые входы которого поступают считанные из накопителя символы 0100, сформисованные в последнем цикле записи информации в данную строку. Сложение помодулю два соответствующих разрядов всех двух наборов проверочных разрядов позволяет вычислить синдром ошибки 1011. который поступает на входы 31 сумматоров блока 32. На другие входы первых двух (I = 2) сумматоров поступает код адреса опрашиваемого разряда (в данном случае 10), на входы других сумматоров – единичный символ. Вследствие этого на всех выходах блока 32 устанавливаются единичные символы, 45 что позволяет через элемент И 34 исправить ошибочный символ его инвертированием в сумматоре 36.

Таким образом, предлагаемое устройство выполняет те же функции, что и известное: осуществляет хранение информации с обнаружением и исправлением ошибок, причем без изменения быстродействия ЗУ. Однако сложность предлагаемого устройства снижается. В известном ЗУ идентификация ошибок и ее коррекция осуществляется го сумматерами вычисления синдрома, блоком анализа отказов, к сумматорами по модулю два, и к управляющими вентилями. В предлагаемом устройстве к каждой строке

накопителя 2 добавляется по одной ячейке (по сравнению с известным устройством. кломе того, идентификация ощибки осуществляется блоками вычисления синдрома и анализа из rn сумматоров по модулю два каждый  $(r_n = r_n + 1)$ , одним многовходовым вентилем, одним сумматором по модулю два и одним управляемым вентилем. Приняв, что один сумматор состоит из трех про-10 стейших логических элементов (реализуется функция  $y = a_1 \bar{a}_2 + \bar{a}_1 a_2$ ), а ЭП (в частности. для статических ЗУ) состоит из четырех таких элементов, производят расчеты аппаратурных затрат в указанных блоках обоих устройств.

Известное устройство: 3. гд вентилей блок 15; к.г. вентилей - блок 26; 3. к вентилей - блок 23; к вентилей - блок 18. т.е. всего  $k(r_0 + h) + 3r_0$  вентилей.

Предлагаемое устройство: 3(rn + 1) вентилей - в блоке 29: 3(rn + 1) вентилей - в блоке 32: один вентиль 34, один вентиль 37 и три вентиля 36, т.е. всего примерно  $4 k + 6(r_0 + 1) + 5$  вентилей.

Приняв, что для кода Хемминга c d = 3 необходимо rn = log2 k + 1 проверочных символов, сопоставляют аппаратурные затраты в первом и втором случаях. При матричной организации накопителя  $(k \times k) k = 2!$ . Исходя из этого, решается неравенство

$$2^{1}(1+5) + 3(1+1) > 4 \cdot 2^{1} + 6(1+2) + 5$$

.

Решение показывает, что неравенство справедливо для всех I ≥ 4, т.е. предлагаемое устройство проще по сравнению с известным для информационной емкости кристалла равной или большей 1 Кбит. Снижение алпаратурных затрат позволяет повысить общую надежность устройства. В этом заключаются технико-экономические преимущества предлагаемого ЗУ перед известным.

## Формула изобретения

40

Запоминающее устройство с автономным контролем, содержащее блок анализа ошибок, основной и дополнительный блоки памяти, входы адреса строк которых соединены соответственно с выходами дешифратора адреса строк, выходы основного и дополнительного блоков памяти соединены с информационными входами основного и дополнительного блоков считывания соответственно, информационный вход основного блока памяти подключен к первому входу первого сумматора по модулю два и является информационным входом устройства, второй вход первого сумматора по модулю два соединен с первым выходом основного блока считывания, выход первого

сумматора по модулю два соединен с первыми входами элементов И группы, вторые входы которых соединены с соответствующими выходами дешифратора адреса разрядов, с входами адреса разрядов основного блока памяти и подключены соответственно к управляющим входам основного блока считывания, выходы которого соединены с первыми входами сумматоров по модулю два группы соответственно, вто- 10 рые входы которых соединены соответственно с выходами элементов И группы, выходы сумматоров по модулю два группы соединены соответственно с информационными входами регистра, выходы которого 15 соединены с входами блока кодирования, выходы которого соединены с информационными входами дополнительного блока памяти и с входами первой группы блока вычисления синдрома, входы второй группы 20 которого соединены с выходами дополнительного блока считывания, управляющие входы основного и дополнительного блоков памяти соединены с выходом блока управления и с управляющим входом блока выда- 25 чи информации, информационный вход

которого соединен с выходом второго сумматора по модулю два, первый вход которого соединен с первым выходом основного блока считывания, входы дешифратора адреса разрядов и дешифратора адреса строк являются адресными входами устройства, входы блока управления являются соответственно первым входом выборки и первым входом разрешения записи устройства, третьи входы элементов И группы объединены и являются вторым входом разрешения записи устройства, вход записи регистра является входом записи устройства, выход блока выдачи информации является информационным выходом устройства, о т л и ч аю щееся тем, что, с целью упрощения по модулю два второй группы объединены и являются вторым входом выборки устройства, вторые входы сумматоров по модулю два первой и второй гоупп соединены соответственно с выходами блока вычисления синдрома, выходы сумматоров по модулю два первой и второй групп соединены с входами элемента И, выход которого соединен с вторым входом второго сумматора по модулю

Редактор А. Козориз

Составитель П. Урбанович Техред М.Моргентал

Корректор С. Шевкун

Заказ 1179

Тираж

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5